# TMC2491A Digital Video Encoder with Macrovision™ Copy Protection

## Features

- Macrovision<sup>™</sup> Copy Protection Signal Processing

- All-Digital Video Encoding

- Internal Digital Synthesizer For Subcarrier Frequency Generation

- 8-Bit Parallel CCIR-601 / SMPTE 170M Format

- Closed Caption Data Insertion

- Switchable Chrominance Bandwidth

- Switchable Pedestal With Gain Compensation

- Pre-Programmed Horizontal And Vertical Timing

- 13.5 Mpps Pixel Rate

- Synchronizes To Incoming Data Stream

- Master Timing Generator Mode

- Internal Interpolation Filters Simplify Output Reconstruction Filters

- 9-Bit D/A Converters For Video Reconstruction

- Supports NTSC And PAL Standards

- Simultaneous S-Video (Y/C) Output

- Controlled Edge Rates

- Parallel And Serial Control Interface

- JTAG (IEEE Std 1149.1-1990) Test Interface

- Single +5V Power Supply

- 44 Lead PLCC Package

## Applications

- Settop Digital Cable Television Receivers

- Settop Digital Satellite Television Receivers

# Description

The TMC2491A video encoder converts digital component video (in 8-bit parallel CCIR-601 or ANSI/SMPTE 125M format) into a standard analog baseband television (NTSC, NTSC-EIA, all PAL standards) signal with a modulated color subcarrier. Both composite (single lead) and S-Video (separate chroma and luma) formats are active simultaneously at the three analog outputs.

The TMC2491A includes all of the features of the TMC2490A Digital Video Encoder, plus Macrovision<sup>™</sup> copy protection signal processing. This datasheet is an addendum to the TMC2490A specification.

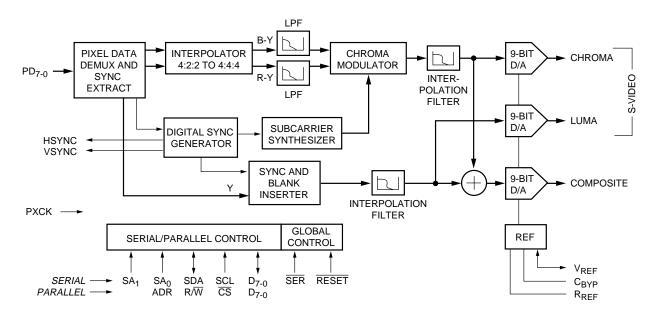

# Block Diagram

## **General Description**

The TMC2491A can modify the analog composite and S-video signal in accordance with the Macrovision copy protection process, Revision 6.1. The outgoing video signal is altered is several ways:

- 1. Color burst inversion

- 2. Pseudo-sync (p-sync) pulses

- 3. AGC pulses

- 4. Back porch pulses before and after vertical sync

- 5. Elevated sync tip and blanking levels

The purpose of these alterations to the standard NTSC and PAL video signals is to render the modified video unrecordable and, therefore, copy protected.

#### **Colorstripe Process**

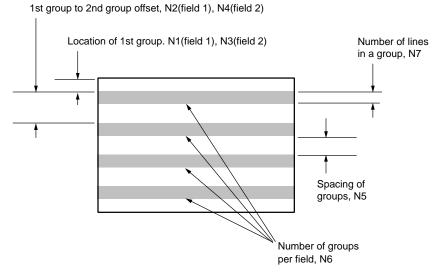

The color burst phase may be inverted for selected lines and groups of lines for odd and even fields (Figure 1). The starting line for each of two groups of lines in each of two fields is controlled via control register values The number of inverted phase lines in each group, the number of groups, and the spacing of groups are also controlled parameters.

A combination of eight bits jointly disable Colorstripe processing when set to a particular state: in all other 255 states, Colorstripe is enabled. To disable Colorstripe, set bit 7 HIGH and bit 6 LOW in registers 10, 11, 12, and 13.

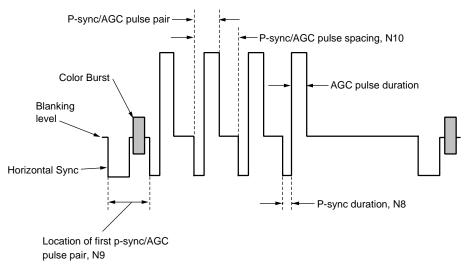

#### Pseudo-Sync (p-sync) and AGC Pulse Pairs

Negative-going "p-sync" pulses extending from blanking to the Macrovision sync level of -30 IRE/-240mV (NTSC/PAL) are inserted on certain lines in the vertical field group. Positive-going "AGC" pulses extending from blanking to 117 IRE/800mV accompany each p-sync pulse. The location, duration, and spacing of these p-sync/AGC pulse pairs are controlled via control register settings. The lines on which the p-sync/AGC pulse pairs are inserted are also selected by the control registers. The duration of the AGC pulse is fixed at 2.7 microseconds. Figure 2 shows a horizontal line with four p-sync/AGC pulse pairs.

Data Transmission mode is a technique for low-bandwidth communication through the presence or absence of the p-sync and AGC pulses. In Data Transmission mode, the p-sync and AGC pulse pairs may be turned off and on independently, and the amplitude of the AGC pulses is limited to 20 IRE/150mV above blanking.

### **Back Porch Pulses**

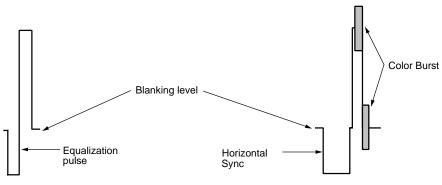

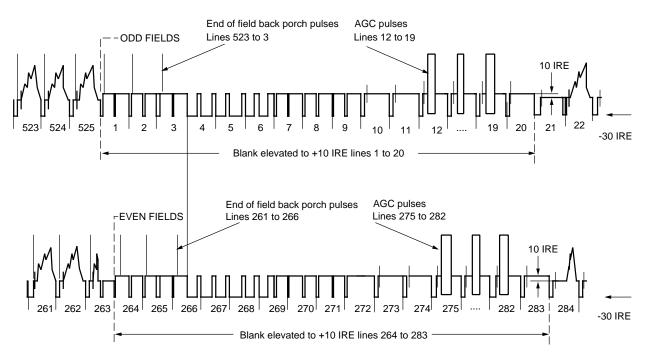

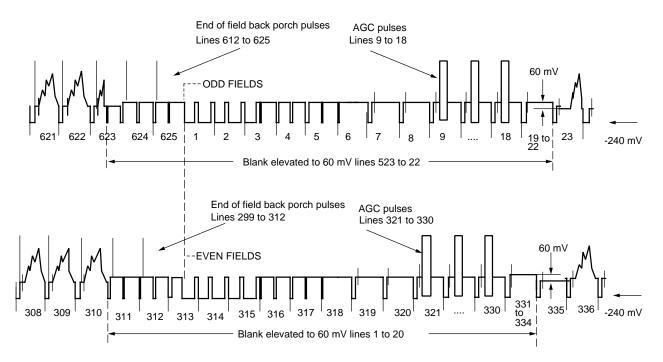

Short pulses at the beginning of back porch segments are inserted on selected lines before and after vertical sync at the end of each field. These "back porch" pulses extend from blanking to 100 IRE/700mV and have a fixed duration of 2 microseconds. When applied to equalization pulses, the "back porch" pulses occur only after equalization pulses that follow the established H timing. Figure 3, Figure 4, and Figure 5 show back porch pulses just after equalization pulses.

Back porch pulses that coincide in time with color burst, shift that portion of the color burst that overlaps the back porch pulse. Figure 3 shows the "split" color burst.

### **Elevated Sync and Blanking**

The TMC2491A can alter the amplitude of sync tips and blanking level. These levels are normally set to -40 and 0 IRE/-300 and 0mV respectively during the vertical blanking interval. The SYNC30 bit in the control register alters all sync tips and vertical interval blanking levels to -30 and +10 IRE/-240 and 60mV respectively (Macrovision defaults). The sync tip and blanking levels for active video lines remain at the standard levels.

Figure 1. Location of Color Stripe Lines And Groups

Figure 3. Back Porch Pulse Detail

## **Control Registers**

The TMC2490A is initialized and controlled by a set of registers which determine the operating modes.

An external controller is employed to write and read the Control Registers through either the 8-bit parallel or 2-line serial interface port. The parallel port, D7-0, is governed by pins  $\overline{CS}$ ,  $R/\overline{W}$ , and ADR. The serial port is controlled by SDA and SCL.

| Reg                               | Bit | Mnemonic           | Function                                                  |  |  |

|-----------------------------------|-----|--------------------|-----------------------------------------------------------|--|--|

| TMC2491A Identification Registers |     |                    |                                                           |  |  |

| 00                                | 7-0 | PARTID2            | (Read only = 94h)                                         |  |  |

| 01                                | 7-0 | PARTID1            | (Read only = 24h)                                         |  |  |

| 02                                | 7-0 | PARTID0            | (Read only = 91h)                                         |  |  |

| 03                                | 7-0 | REVID              | (Read only = revision #)                                  |  |  |

|                                   |     | Encoder C          | Control Registers                                         |  |  |

| 04-0F                             | 7-0 | Controls           | Same as in TMC2490                                        |  |  |

|                                   |     | Macrovision        | Control Registers                                         |  |  |

| 10                                | 7-6 | DBI <sub>7-6</sub> | Phase inversion enable bits                               |  |  |

| 10                                | 5-0 | N1                 | 1st inverse phase line, 1st<br>group, 1st field           |  |  |

| 11                                | 7-6 | DBI <sub>5-4</sub> | Phase inversion enable bits                               |  |  |

| 11                                | 5-0 | N2                 | 1st inverse phase group to 2nd group offset, 1st field    |  |  |

| 12                                | 7-6 | DBI <sub>3-2</sub> | Phase inversion enable bits                               |  |  |

| 12                                | 5-0 | N3                 | 1st inverse phase line, 1st<br>group, 2nd field           |  |  |

| 13                                | 7-6 | DBI <sub>1-0</sub> | Phase inversion enable bits                               |  |  |

| 13                                | 5-0 | N4                 | 1st inverse phase group to<br>2nd group offset, 2nd field |  |  |

| 14                                | 7-6 | N7                 | No. lines per stripe group                                |  |  |

| 14                                | 5-3 | N6                 | Number of phase inversion groups per field                |  |  |

| 14                                | 2-0 | N5                 | Phase inversion group spacing                             |  |  |

| 15                                | 7-6 | reserved           |                                                           |  |  |

| 15                                | 5-3 | N8A                | P-sync duration, A                                        |  |  |

| 15                                | 2-0 | N8B                | P-sync duration, B                                        |  |  |

## Table 1. Control Register Map — Changes/Additions to the TMC2490

| Reg | Bit | Mnemonic       | Function                            |  |

|-----|-----|----------------|-------------------------------------|--|

| 16  | 7   | PULSE          | Pulse / static select               |  |

| 16  | 6   | reserved       |                                     |  |

| 16  | 5-3 | N9A            | P-sync/AGC location, A              |  |

| 16  | 2-0 | N9B            | P-sync/AGC location, B              |  |

| 17  | 7   | reserved       |                                     |  |

| 17  | 6   | SYNC30         | Sync tip and blanking level         |  |

| 17  | 5-3 | N10A           | P-sync/AGC spacing, A               |  |

| 17  | 2-0 | N10B           | P-sync/AGC spacing, B               |  |

| 18  | 7-0 | XMIT           | Data transmit mode                  |  |

| 19  | 7   | reserved       |                                     |  |

| 19  | 6-0 | PSPAGC<br>14-8 | P-sync/AGC line enable,<br>MSBs     |  |

| 1A  | 7-0 | PSPAGC<br>7-0  | P-sync/AGC line enable,<br>LSBs     |  |

| 1B  | 7-0 | PSAGAB<br>14-8 | P-sync/AGC pattern select A/B, MSBs |  |

| 1C  | 7-0 | PSAGAB<br>7-0  | P-sync/AGC pattern select A/B, LSBs |  |

| 1D  | 7-0 | PSAGPATA       | P-sync/AGC pattern A                |  |

| 1E  | 7-0 | PSAGPATB       | P-sync/AGC pattern B                |  |

| 1F  | 7-4 | BPP1           | Pulsed lines before VSYNC           |  |

| 1F  | 3-0 | BPP2           | Pulsed lines after VSYNC            |  |

#### Notes:

1. Functions are listed in the order of reading and writing.

2. For each register listed above, all bits not specified are reserved and should be set to zero to ensure proper operation.

| <b>TMC</b><br>00<br>01<br>02 |                   | PARTID2<br>PARTID1<br>PARTID0 | Function<br>eation Registers (Read only)<br>(Read only = 78h)<br>(Read only = 38h)<br>(Read only = 91h)                                                                                                                                                                                                                           |

|------------------------------|-------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00<br>01<br>02               | 7-0<br>7-0<br>7-0 | PARTID2<br>PARTID1<br>PARTID0 | (Read only = 78h)<br>(Read only = 38h)                                                                                                                                                                                                                                                                                            |

| 01<br>02                     | 7-0<br>7-0        | PARTID1<br>PARTID0            | (Read only = 38h)                                                                                                                                                                                                                                                                                                                 |

| 02                           | 7-0               | PARTID0                       | · · ·                                                                                                                                                                                                                                                                                                                             |

|                              |                   |                               |                                                                                                                                                                                                                                                                                                                                   |

|                              |                   | REVID                         | (Read only = 911)<br>(Read only = revision #)<br>This specification applies to<br>TMC2491A circuits with REVID<br>>= to 02h. See revision B of<br>this document for circuits with<br>REVID - 01h.                                                                                                                                 |

|                              |                   | Encoder (                     | Control Registers                                                                                                                                                                                                                                                                                                                 |

| 04-0F                        | 7-0               | Controls                      | Same as in TMC2490                                                                                                                                                                                                                                                                                                                |

|                              |                   | Macrovisio                    | n Control Registers                                                                                                                                                                                                                                                                                                               |

| 10                           | 7-6               | DBI <sub>7-6</sub>            | Phase inversion enable bits.<br>Subcarrier phase inversion on<br>a line group-by-line group<br>basis is enabled whenever<br>DBI7-0 is not set equal to AAh.                                                                                                                                                                       |

| 10                           | 5-0               | N1                            | The 6-bit N1 value determines<br>the location of the 1st phase<br>inversion line of the 1st group<br>of inverse phase lines in the 1st<br>field. The position of this line<br>can be from 1 to 64 lines from<br>VSYNC. The default value for<br>N1 is 18 (22h) for NTSC and 48<br>(30h) for PAL.                                  |

| 11                           | 7-6               | DBI <sub>5-4</sub>            | Phase inversion enable bits                                                                                                                                                                                                                                                                                                       |

| 11                           | 5-0               | N2                            | The 6-bit N2 value determines<br>the offset of the 2nd group of<br>inverse phase lines with<br>respect to the start of the 1st<br>group in the 1st field. The<br>position of this line can be from<br>1 to 64 lines from the start of<br>the 1st group. The default<br>value for N2 is 20 (14h) for<br>NTSC and 32 (20h) for PAL. |

| 12                           | 7-6               | DBI <sub>3-2</sub>            | Phase inversion enable bits                                                                                                                                                                                                                                                                                                       |

| 12                           | 5-0               | N3                            | The 6-bit N3 value determines<br>the location of the 1st phase<br>inversion line of the 1st group<br>of inverse phase lines in the<br>2nd field. The position of this<br>line can be from 1 to 64 lines<br>from VSYNC. The default<br>value for N3 is 18 (22h) for<br>NTSC and 48 (30h) for PAL.                                  |

| 13                           | 7-6               | DBI <sub>1-0</sub>            | Phase inversion enable bits                                                                                                                                                                                                                                                                                                       |

## Table 2. Control Register Definitions — Changes/Additions to the TMC2490A

| Reg | Bit | Mnemonic | Function                                                                                                                                                                                                                                                                                                                          |  |  |

|-----|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 13  | 5-0 | N4       | The 6-bit N4 value determines<br>the offset of the 2nd group of<br>inverse phase lines with<br>respect to the start of the 1st<br>group in the 2nd field. The<br>position of this line can be from<br>1 to 64 lines from the start of<br>the 1st group. The default<br>value for N2 is 20 (14h) for<br>NTSC and 32 (20h) for PAL. |  |  |

| 14  | 7-6 | N7       | The number of phase inversion<br>lines per group varies by (2 +<br>N7). The 2-bit N7 value allows<br>the number of inverse phase<br>lines per group to vary from 2 to<br>5. The default value for N7 is 2<br>(0 in data mode).                                                                                                    |  |  |

| 14  | 5-3 | N6       | The number of phase inversion<br>groups per field varies by<br>(6+N6). The 3-bit N6 value<br>allows the number of groups<br>per field to vary from 6 to 13.<br>The default value for N6 is 4 for<br>NTSC and 3 for PAL.                                                                                                           |  |  |

| 14  | 2-0 | N5       | The spacing of groups varies<br>by (16+N5) for NTSC and<br>(12+N5) for PAL. The 3-bit N5<br>value allows the spacing of<br>groups to vary from 16 to 23 for<br>NTSC and from 12 to 19 for<br>PAL. The default value for N5<br>is 4.                                                                                               |  |  |

| 15  | 7-6 | reserved |                                                                                                                                                                                                                                                                                                                                   |  |  |

| 15  | 5-3 | N8A      | The A-pattern duration of p-<br>sync/AGC pulse pairs varies<br>by:<br>(24+(2xN8A)) for NTSC and<br>(16+(2xN8A)) for PAL. The<br>3-bit N8A value allows the<br>duration of p-sync/AGC pulse<br>pairs to vary from 24 to 38 for<br>NTSC and from 16 to 30 for<br>PAL. The default value for N8A<br>is 3 for NTSC and 4 for PAL.     |  |  |

| 15  | 2-0 | N8B      | The B-pattern duration of<br>p-sync/AGC pulse pairs varies<br>by:<br>(24+(2xN8B)) for NTSC and<br>(16+(2xN8B)) for PAL. The 3-<br>bit N8B value allows the<br>duration of P-sync/AGC pulse<br>pairs to vary from 24 to 38 for<br>NTSC and from 16 to 30 for<br>PAL. The default value for N8B<br>is 0 for NTSC and PAL.           |  |  |

| Reg | Bit | Mnemonic | Function                                                                                                                                                                                                                                                                                                                    |

|-----|-----|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16  | 7   | PULSE    | Pulse / static select. When<br>HIGH, the AGC pulse<br>amplitudes varies in<br>accordance with Macrovision<br>specifications. When LOW, the<br>amplitude of the AGC pulses is<br>constant.                                                                                                                                   |

| 16  | 6   | reserved |                                                                                                                                                                                                                                                                                                                             |

| 16  | 5-3 | N9A      | The A-pattern location of<br>p-sync/AGC pulse pairs varies<br>by:<br>(96+(8xN9A)) for NTSC and<br>PAL. The 3-bit N9A value<br>allows the location of p-sync/<br>AGC pulse pairs to vary from<br>96 to 152. The default value for<br>N9A is 2 for NTSC and 3 for<br>PAL.                                                     |

| 16  | 2-0 | N9B      | The B-pattern location of p-<br>sync/AGC pulse pairs varies<br>by:<br>(96+(8xN9B)) for NTSC and<br>PAL. The 3-bit N9B value<br>allows the location of p-sync/<br>AGC pulse pairs to vary from<br>96 to 152. The default value for<br>N9B is 0 for NTSC and PAL.                                                             |

| 17  | 7   | reserved |                                                                                                                                                                                                                                                                                                                             |

| 17  | 6   | SYNC30   | When HIGH, sync tip and<br>blanking levels are elevated<br>+10 IRE to -30 and +10 IRE<br>respectively, during the vertical<br>blanking interval only. When<br>LOW, sync tip and blanking<br>levels are at their normal levels<br>of -40 and 0 IRE respectively.<br>Macrovision default = 1.                                 |

| 17  | 5-3 | N10A     | The A-pattern spacing of p-<br>sync/AGC pulse pairs varies<br>by:<br>(88+(8xN10A)) for NTSC and<br>(56+(8xN10A)) for PAL. The<br>3-bit N10A value allows the<br>spacing of p-sync/AGC pulse<br>pairs to vary from 88 to 144 for<br>NTSC and from 56 to 112 for<br>PAL. The default value for<br>N10A is 3 for NTSC and PAL. |

| Reg | Bit | Mnemonic       | Function                                                                                                                                                                                                                                                                                                                                                           |  |

|-----|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 17  | 2-0 | N10B           | The B-pattern spacing of<br>p-sync/AGC pulse pairs varie<br>by:<br>(88+(8xN10B)) for NTSC and<br>(56+(8xN10B)) for PAL. The<br>3-bit N10B value allows the<br>spacing of p-sync/AGC pulse<br>pairs to vary from 88 to 144 for<br>NTSC and from 56 to 112 for<br>PAL. The default value for<br>N10B is 0 for NTSC and PAL                                           |  |

| 18  | 7-0 | XMIT           | Data transmit mode is enabled<br>when register 18 = D1h. When<br>data transmit mode is selected,<br>AGC pulses are limited in<br>amplitude to +20 IRE/150mV.<br>Normal Macrovision pulse<br>levels occur for all other<br>combinations.                                                                                                                            |  |

| 19  | 7   | reserved       |                                                                                                                                                                                                                                                                                                                                                                    |  |

| 19  | 6-0 | PSPAGC<br>14-8 | P-sync/AGC line enable,<br>MSBs. Each bit of<br>PSPAGC <sub>14-0</sub> enables<br>P-sync/AGC pulse pairs for<br>one line in each field. Bit N<br>enables line (N + 7) and (N +<br>270) for N = 0 to 14. In PAL,<br>(N + 7) and (N + 319) will have<br>P-sync/AGC pulse pairs. The<br>default value for register 19 is<br>3 (03h) for NTSC and 31 (1Fh)<br>for PAL. |  |

| 1A  | 7-0 | PSPAGC<br>7-0  | P-sync/AGC line enable, LSBs.<br>The default value for register<br>1A is 252 (FCh) for NTSC and<br>248 (F8h) for PAL.                                                                                                                                                                                                                                              |  |

| 1B  | 7   | reserved       |                                                                                                                                                                                                                                                                                                                                                                    |  |

| 1B  | 6-0 | PSAGAB<br>14-8 | P-sync/AGC pattern A/B<br>select, MSBs. Each bit of<br>PSAGAB <sub>14-0</sub> selects P-sync/<br>AGC pattern A (HIGH) or B<br>(LOW) for one line per field.<br>Mapping precisely matches<br>that of PSPAGC <sub>14-0</sub> . Default is<br>7FFFh, which selects pattern A<br>on all lines.                                                                         |  |

| 1C  | 7-0 | PSAGAB<br>7-0  | P-sync/AGC pattern A/B<br>select, LSBs. Each bit of<br>PSAGAB <sub>14-0</sub> selects P-sync/<br>AGC pattern A (HIGH) or B<br>(LOW) for one line per field.<br>Mapping precisely matches<br>that of PSPAGC <sub>14-0</sub> . Default is<br>7FFFh, which selects pattern A<br>on all lines.                                                                         |  |

| Reg | Bit | Mnemonic | Function                                                                                                                                                                                                                                                                              |

|-----|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1D  | 7-0 | PSAGPATA | P-sync/AGC pattern A. These<br>8 bits determine which of up to<br>8 p-sync/AGC pulse pairs are<br>enabled or suppressed for<br>each line. If the Nth bit is<br>HIGH, the Nth pulse pair will be<br>active. If the Nth bit is LOW,<br>the Nth p-sync pulse pair will<br>be suppressed. |

| 1E  | 7-0 | PSAGPATB | P-sync/AGC pattern B. These<br>8 bits determine which of up to<br>8 p-sync/AGC pulse pairs are<br>enabled or suppressed for<br>each line. If the Nth bit is<br>HIGH, the Nth pulse pair will be<br>active. If the Nth bit is LOW,<br>the Nth p-sync pulse pair will<br>be suppressed. |

| Reg | Bit | Mnemonic | Function                                                                                                        |

|-----|-----|----------|-----------------------------------------------------------------------------------------------------------------|

| 1F  | 7-4 | BPP1     | This 4-bit value determines the<br>number of lines before VSYNC<br>that have back porch pulses.<br>See Table 3. |

| 1F  | 3-0 | BPP2     | This 4-bit value determines the<br>number of lines after VSYNC<br>that have back porch pulses.<br>See Table 3.  |

Figure 4. 525/60 (NTSC, PAL-M) Vertical Interval With Macrovision Copy Protection Process

|                    | NT                                     | SC                            | PAL                               |                               |  |

|--------------------|----------------------------------------|-------------------------------|-----------------------------------|-------------------------------|--|

| BPP<br>4-bit value | BPP1<br>lines before VSYNC             | BPP2<br>lines after VSYNC     | BPP1<br>lines before VSYNC        | BPP2<br>lines after VSYNC     |  |

| 0                  | none                                   | none                          | none                              | none                          |  |

| 1                  | 3, 266                                 | 7, 270                        | 312, 625                          | 4, 316                        |  |

| 2                  | 2, 3, 255, 266                         | 7, 8, 270, 271                | 311, 312, 624, 625                | 4, 5, 316, 317                |  |

| 3                  | 1-3, 264-266                           | 7-9, 270-272                  | 310-312, 623-625                  | 4-6, 316-318                  |  |

| 4                  | 525, 1-3, 263-266                      | 7-10, 270-273                 | 309-312, 622-625                  | 4-7, 316-319                  |  |

| N                  | (529-N) to 525, 1-3,<br>(267-N) to 266 | 7 to (6+N),<br>270 to (269+N) | (313-N) to 312,<br>(626-N) to 625 | 4 to (3+N),<br>316 to (315+N) |  |

|          | Enabled                    |     |          |     | Disabled |       |

|----------|----------------------------|-----|----------|-----|----------|-------|

|          | NTSC<br>(Power-Up Default) |     | PAL      |     | NTSC/PAL |       |

| Register | Binary                     | HEX | Binary   | HEX | Binary   | HEX   |

| 10       | 11010010                   | D2  | 10110000 | B0  | 10XXXXXX | 8X-BX |

| 11       | 10010100                   | 94  | 10100000 | A0  | 10XXXXXX | 8X-BX |

| 12       | 00010010                   | 12  | 10110000 | B0  | 10XXXXXX | 8X-BX |

| 13       | 11010100                   | D4  | 10100000 | A0  | 10XXXXXX | 8X-BX |

| 14       | 10100100                   | A4  | 10011100 | 9C  | 00000000 | 00    |

| 15       | 00011000                   | 18  | 00100000 | 24  | 00XXXXXX | 0X-3X |

| 16       | 10010000                   | 90  | 10011000 | 9B  | 0000000  | 00    |

| 17       | 01011 00                   | 58  | 11011000 | DB  | 0000000  | 00    |

| 18       | 01000000                   | 40  | 00000000 | 00  | 00000000 | 00    |

| 19       | 00000011                   | 03  | 00011111 | 1F  | 0000000  | 00    |

| 1A       | 11111100                   | FC  | 11111000 | F8  | 0000000  | 00    |

| 1B       | 11110000                   | F0  | 11111100 | FC  | 0000000  | 00    |

| 1C       | 11110000                   | F0  | 11111100 | FC  | 00000000 | 00    |

| 1D       | 00000000                   | 00  | 00000000 | FC  | 00000000 | 00    |

| 1E       | 00000000                   | 00  | 00000000 | FC  | 00000000 | 00    |

| 1F       | 01100011                   | 60  | 01110111 | 77  | 00000000 | 00    |

## Table 4. Default Parameters For Macrovision Copy Protection Process

## **Ordering Information**

| Product Number | Temperature Range | Screening  | Package      | Package Marking |

|----------------|-------------------|------------|--------------|-----------------|

| TMC2491AR2C    | 0°C to 70°C       | Commercial | 44-Lead PLCC | 2491AR2C        |

All parameters contained in this specification are guaranteed by design, characterization, sample testing or 100% testing as appropriate. CADEKA reserves the right to change products and specifications without notice. This information does not convey any license under patent rights of CADEKA or others.

#### For Further Assistance:

Exar Corporation Headquarters and Sales Offices 48720 Kato Road Fremont, CA 94538 - USA

Tel.: +1 (510) 668-7000 Fax: +1 (510) 668-7001 www.exar.com

#### NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

©2013 Exar Corporation