Dec 2010

#### **FEATURES**

- Low Power CMOS Technology

- All Receiver and Transmitter Inputs and Outputs are TTL Compatible

- Transmitter Inhibits Bipolar Violation Insertion for Transmission of Alarm Conditions

- Alarm Output Indicates Loss of Received Bipolar Violations

- Up to 125µs Variance of Data Transfer Timing in Both Transmit and Receive Paths Allows Operation in Plesiochronous Networks

- Both Receiver and Transmitter Perform Byte Insertion or Deletion in Response to Local Clock Slips

#### **APPLICATIONS**

- CCITT G.703 Compliant 64kbps Codirectional Interface

- Performs the Digital and Analog Functions for a Complete 64kbps Data Adaption Unit (DAU) When Used With the XR-T6164

#### **GENERAL DESCRIPTION**

The XR-T6165 is a CMOS device which contains the digital circuitry necessary to interface both directions of a 64kbps data stream to 2.048Mbps transmit and receive PCM time-slots. The XR-T6165 and the companion XR-T6164 line interface chip together form a CCITT G.703 compliant 64kbps codirectional interface.

The XR-T6165 contains separate transmit and receive

sections. The transmitter transforms 8 bit serial data from a 2.048Mbps time-slot into an encoded 64kbps data stream. The receiver , which performs the reverse operation, decodes the 64kbps data, extracts a clock signal, and then outputs the data to a 2.048Mbps time-slot. The XR-T6165 provides features which allow the repetitions and deletions of both received and transmitted data as clock skews and transients occur.

# **ORDERING INFORMATION**

| Part No.   | Package                    | Operating<br>Temperature Range |  |  |

|------------|----------------------------|--------------------------------|--|--|

| XR-T6165CD | 24 Lead 300 Mil JEDEC SOIC | 0°C to +70°C                   |  |  |

| XR-T6165ID | 24 Lead 300 Mil JEDEC SOIC | −40°C to +85°C                 |  |  |

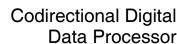

Figure 1. XR-T6165 Transmit Section Block Diagram

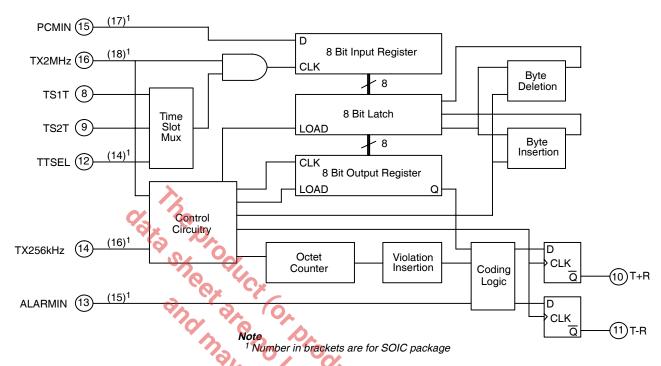

Figure 2. XR-T6165 Receiver Section Block Diagram

**TOM**

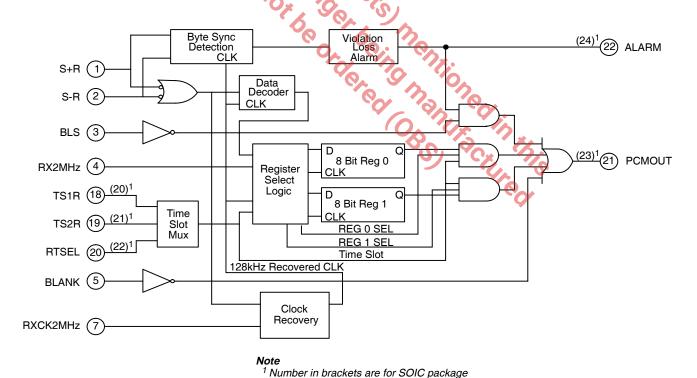

## **PIN CONFIGURATION**

24 Lead SOIC (JEDEC, 0.300")

# **PIN DESCRIPTION**

|         |                                                                                                   |          |      | T+R   10   15   ALARMIN T-R   11   14   TTSEL                                                                       |  |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------|----------|------|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

|         |                                                                                                   |          | λ    | NC 12 13 NC                                                                                                         |  |  |  |  |  |  |  |

|         | 24 Lead SOIC (JEDEC, 0.300")                                                                      |          |      |                                                                                                                     |  |  |  |  |  |  |  |

|         |                                                                                                   |          |      |                                                                                                                     |  |  |  |  |  |  |  |

|         | 24 Lead SOIC (JEDEC, 0.300")  PIN DESCRIPTION  DIP Pin # SOIC Pin # Description  Type Description |          |      |                                                                                                                     |  |  |  |  |  |  |  |

|         | no 440                                                                                            |          |      |                                                                                                                     |  |  |  |  |  |  |  |

| DIN DEG | PIN DESCRIPTION                                                                                   |          |      |                                                                                                                     |  |  |  |  |  |  |  |

| PIN DES | PIN DESCRIPTION                                                                                   |          |      |                                                                                                                     |  |  |  |  |  |  |  |

| DIP     | SOIC                                                                                              | Symbol   | Туре | Description                                                                                                         |  |  |  |  |  |  |  |

| Pin #   | Pin #                                                                                             |          |      |                                                                                                                     |  |  |  |  |  |  |  |

| 1       | 1                                                                                                 | S+R      | I    | Positive AMI Data to Receiver. Positive data from the XR-T6164 receive-side. Active low.                            |  |  |  |  |  |  |  |

| 2       | 2                                                                                                 | S-R      | I    | <b>Negative AMI Data to Receiver.</b> Negative data from the XR-T6164 receive-side. Active low.                     |  |  |  |  |  |  |  |

| 3       | 3                                                                                                 | BLS      | I    | Byte Locking Supervision. When active, causes blanking of PCMOUT under received alarm conditions. Active low.       |  |  |  |  |  |  |  |

| 4       | 4                                                                                                 | RX2MHz   | I    | Receiver 2.048MHz Clock. Used to clock out PCM data.                                                                |  |  |  |  |  |  |  |

| 5       | 5                                                                                                 | BLANK    | I    | PCMOUT Data Blanking. When active, forces PCMOUT data to all ones (AIS). Active high.                               |  |  |  |  |  |  |  |

| 6       | 6                                                                                                 | $V_{DD}$ |      | +5V <u>+</u> 10% Power Source.                                                                                      |  |  |  |  |  |  |  |

| 7       | 7                                                                                                 | RXCK2MHz | I    | 2.048MHz Clock. Used by receiver clock recovery circuit.                                                            |  |  |  |  |  |  |  |

| 8       | 8                                                                                                 | TS1T     | I    | Transmitter time-slot 1 Input.                                                                                      |  |  |  |  |  |  |  |

| 9       | 9                                                                                                 | TS2T     | 1    | Transmitter time-slot 2 Input.                                                                                      |  |  |  |  |  |  |  |

| 10      | 10                                                                                                | T+R      | 0    | Transmit Positive AMI Data Output. Data to XR-T6164 positive transmitter input. Active low                          |  |  |  |  |  |  |  |

| 11      | 11                                                                                                | T-R      | 0    | <b>Transmit Negative AMI Data Output.</b> Data to XR-T6164 negative transmitter input. Active low.                  |  |  |  |  |  |  |  |

|         | 12                                                                                                | NC       |      | No Connect.                                                                                                         |  |  |  |  |  |  |  |

|         | 13                                                                                                | NC       |      | No Connect.                                                                                                         |  |  |  |  |  |  |  |

| 12      | 14                                                                                                | TTSEL    | I    | <b>Transmit time-slot Select</b> . When high, TS1T is selected; when low, TS2T is selected.                         |  |  |  |  |  |  |  |

| 13      | 15                                                                                                | ALARMIN  | I    | Alarm Input. When active, inhibits insertion of violations used for octet timing in transmitter output. Active high |  |  |  |  |  |  |  |

| 14      | 16                                                                                                | TX256kHz | I    | Transmitter 256kHz Clock. Used to output 64kbps encoded data.                                                       |  |  |  |  |  |  |  |

# PIN DESCRIPTION (CONT'D)

| DIP<br>Pin # | SOIC<br>Pin# | Symbol   | Туре | Description                                                                                                                 |

|--------------|--------------|----------|------|-----------------------------------------------------------------------------------------------------------------------------|

| 15           | 17           | PCMIN    | I    | Transmit PCM Input. Data read from the system PCM bus.                                                                      |

| 16           | 18           | TX2MHz   | ı    | Transmitter 2.048MHz Clock. Clocks PCM data in PCMIN.                                                                       |

| 17           | 19           | $V_{SS}$ |      | Ground.                                                                                                                     |

| 18           | 20           | TS1R     | I    | Receiver time-slot 1 Input.                                                                                                 |

| 19           | 21           | TS2R     | 1    | Receiver time-slot 2 Input.                                                                                                 |

| 20           | 22           | RTSEL    | I    | Receive time-slot Select. When high, TS1R is selected; when low, TS2R is selected.                                          |

| 21           | 23           | PCMOUT   | o    | Received PCM Output Data. Data sent to the system PCM bus.                                                                  |

| 22           | 24           | ALARM    | 60   | Octet Timing Alarm. When active, indicates loss of received bipolar violations that are used for octet timing. Active high. |

# **ELECTRICAL CHARACTERISTICS**

Test Conditions:  $V_{DD} = 5V \pm 10\%$ ,  $T_A = 25^{\circ}C$ , Unless Otherwise Specified

| Symbol                        | Parameter                                                               | Min.  | Тур.     | Max.          | Unit | Conditions             |  |  |

|-------------------------------|-------------------------------------------------------------------------|-------|----------|---------------|------|------------------------|--|--|

| DC Electrical Characteristics |                                                                         |       |          |               |      |                        |  |  |

| V <sub>IH</sub>               | Logic 1                                                                 | 2.4   |          |               | V    |                        |  |  |

| $V_{IL}$                      | Logic 0                                                                 |       |          | 0.4           | V    |                        |  |  |

| $V_{DD}$                      | Supply                                                                  | 4.5   |          | 5.5           | V    |                        |  |  |

| I <sub>DD</sub>               | Supply Current                                                          |       | 500      |               | μΑ   | Dynamic Supply Current |  |  |

| I <sub>IL</sub>               | Input Leakage                                                           |       |          | 1             | μΑ   |                        |  |  |

| V <sub>OL</sub>               | <b>&gt;</b> .                                                           |       |          | 0.4           | V    | At 1.6mA               |  |  |

| V <sub>OH</sub>               | or he                                                                   | 2.4   |          |               | V    | At 0.4mA               |  |  |

| AC Electrica                  | I Characteristics                                                       |       | •        |               |      |                        |  |  |

| General                       | 9,0,00                                                                  |       |          |               |      |                        |  |  |

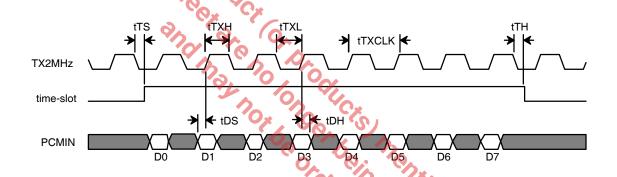

| tr, tf                        | Output Rise/Fall Time                                                   |       |          | 20            | ns   | All Outputs            |  |  |

| Receiver                      | · C×                                                                    | Cir   |          |               |      |                        |  |  |

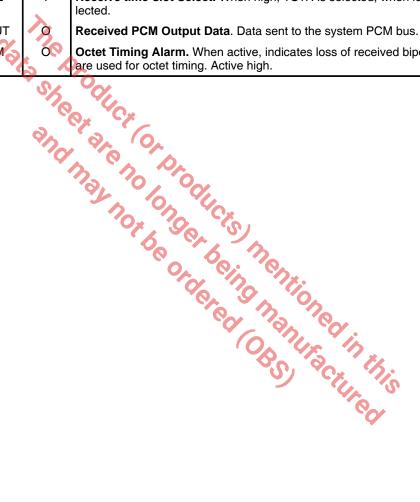

| tRS                           | RX2MHz Rising Edge to TS<br>Rising Edge Set Up Time                     | 0     | <b>5</b> | tRXL -<br>100 | ns   | Figure 3               |  |  |

| tRH                           | RX2MHz Rising Edge to TS Falling Edge Hold Time                         | 78    | 100%     | tRXL -<br>100 | ns   | Figure 3               |  |  |

| tDRS                          | TS Rising Edge to Leading Edge of PCMOUT D0 Bit Delay                   | 20,0  | 20,46    | 10            | ns   | Figure 3               |  |  |

| tDRH                          | TS Falling Edge to Trailing Edge of PCMOUT D7 Bit Hold Time             | 0,000 | Op 6     | -10           | ns   | Figure 3               |  |  |

| tRXD                          | RX2MHz Rising Edge to<br>PCMOUT Bits D1 Through D6<br>Rising Edge Delay |       | Order    | 10            | ns   | Figure 3               |  |  |

| tPW                           | PCMOUT Pulse Width                                                      |       | 488      | 0             | ns ( | Figure 3               |  |  |

| tRXH                          | RX2MHz High Time                                                        |       | 244      | 6             | ns   | Figure 3               |  |  |

| tRXL                          | RX2MHz Low Time                                                         |       | 244      | S             | ns 🔿 | Figure 3               |  |  |

| tRXCLK                        | RX2MHz Period                                                           |       | 488      | · '           | ns   | <u>±</u> 100ppm        |  |  |

| Transmitter                   |                                                                         |       |          |               |      |                        |  |  |

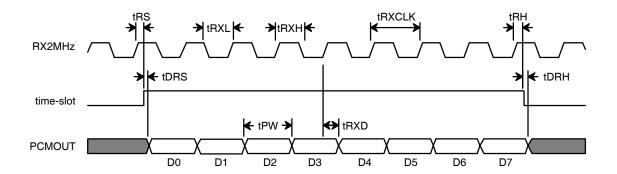

| tTS                           | TS Rising Edge to TX2MHz Set Up Time                                    | 20    |          | tTXL -<br>100 | ns   | Figure 4               |  |  |

| tTH                           | TS Falling Edge to TX2MHz Hold Time                                     | 0     |          | tTXL -<br>100 | ns   | Figure 4               |  |  |

| tDS                           | PCMIN Edge to TX2MHz Set Up Time                                        | 100   |          |               | ns   | Figure 4               |  |  |

| tDH                           | PCMIN Edge to TX2MHz Hold<br>Time                                       | 100   |          |               | ns   | Figure 4               |  |  |

| tTXH                          | TX2MHz High Time                                                        |       | 244      |               | ns   | Figure 4               |  |  |

# **ELECTRICAL CHARACTERISTICS (CONT'D)**

| Symbol       | Parameter                              | Min. | Тур.   | Max. | Unit | Conditions |  |  |

|--------------|----------------------------------------|------|--------|------|------|------------|--|--|

| AC Electrica | AC Electrical Characteristics (Cont'd) |      |        |      |      |            |  |  |

| Transmitter  | Transmitter (Cont'd)                   |      |        |      |      |            |  |  |

| tTXL         | TX2MHz Low Time                        |      | 244    |      | ns   | Figure 4   |  |  |

| tTXCLK       | TX2MHz Period                          |      | 488    |      | ns   | Figure 4   |  |  |

| tKXH         | TX256kHz High Time                     |      | 1.95   |      | μS   |            |  |  |

| tKXL         | TX256kHz Low Time                      |      | 1.95   |      | μS   |            |  |  |

| tKXCLK       | TX256kHz Period                        |      | 3.9063 |      | μS   |            |  |  |

Specifications are subject to change without notice

# **ABSOLUTE MAXIMUM RATINGS**

# **Magnetic Supplier Information:**

Pulse Telecom Product Group P.O. Box 12235 San Diego, CA 92112 Tel. (619)674-8100 Fax. (619)674-8262 Transpower Technologies, Inc. 24 Highway 28, Suite 202 Crystal Bay, NV 89402-0187 Tel. (702) 831-0140 Fax. (702) 831-3521

Figure 3. Receive Time-slot Timing

Figure 4. Transmit Time-slot Timing

Figure 5. Clock Timing

#### SYSTEM DESCRIPTION

# **Transmitter**

Figure 1 shows the XR-T6165 transmitter section block diagram. The transmitter converts eight bit bursts or octets of 2.048Mbps serial data present in a PCM time-slot to a coded continuous 64kbps data stream. During operation, data input is controlled by external clock and time-slot signals, and the 64kbps data output is timed by an external 256kHz clock. Since the input and output rates may not be exactly equal because of slight clock rate dif ferences, periodic slips can occur. Therefore, circuitry is included to delete or repeat octets, if necessary. Transmitter operation is as follows. Pin numbers, refer to the DIP package.

PCM data is applied to PCMIN (pin 15), a 2.048MHz local clock is applied to TX2MHz (pin 16), and a time-slot signal is applied through the time-slot multiplexer multiplexer allows the transmitter to be hard wired to two time-slot positions. A time-slot signal is applied to multiplexer inputs TS1T (pin 8) or TS2T (pin 9), and a time-slot select logic level is applied to TTSEL (pin 12). A high level at TTSEL selects TS1T while a low level enables TS2T. The time-slot is an envelope derived externally from TX2MHz that covers eight clock pulses The rising edge of the time-slot signal should be made to coincide with the falling edge of TX2MHz. Eight bits of PCM data are clocked into the transmitter input register on the rising edge of TX2MHz while the selected time-slot signal is high. The input register data is then transferred to a storage latch.

Transmission of 64kbps data is controlled by the 256kHz local clock that is applied to TX256kHz (pin 14). It is not necessary for this clock to be synchronized with any other signals that are applied to the transmitter . The output process begins by transferring data from the storage latch to the output shift register after transmission of the previous eight bits of data is complete. Four periods of TX256kHz are required to encode each data bit. A "logic 0" applied to PCMIN is coded as 0101 while a "logic 1" is coded as 0011. This data is output on either T+R (pin 10) or T-R (pin 1 1) according to the AMI (alternate mark inversion) coding rule. Note that the T+R and-R outputs as well as the corresponding XR-T6164 transmitteinputs (TX+I/P, TX-I/P) are all active-low. Therefore, a "logic 0" is coded as a 1010 and a "logic 1" as a 1100 at the bipolar

transmitter output as specified by CCITT G.703. Transmission of octet timing is performed by feeding the seventh and eighth data bits in each word to the same transmitter output. This function may be inhibited by setting ALARMIN (pin 13) high to transmit an alarm condition. Should skew occur between the TX2MHz and TX256kHz clocks signals, or during an adjustment of the timing of the time-slot signal, circuitry is included to delete or repeat complete words of data. This could happen, for example, when changing from one time-slot position to another. A byte repetition or insertion occurs once if no new PCM data is received. A byte repetition just occurs once. If no new PCM data is received, the T+R and T-R outputs stay high. A byte deletion occurs when the transmitter receives a new byte of data before the previous byte is transferred from the storage latch to the output register. Under this condition, the stored data is overwritten.

#### Receiver

Figure 2 shows the block diagram of the XR-T6165 receiver section. The receiver converts coded continuous 64kbps data to eight bit bursts of 2.048Mbps serial data suitable for insertion in a PCM time-slot. During operation, data input is timed by a clock that is extracted from the input signal, while output is controlled by external locally supplied clock and time-slot signals. Since the data input and output rates may not be exactly equal, circuitry is included to delete or repeat eight bit data blocks, if necessary. Receiver operation is as follows. A line interface chip such as the receive section of the XR-T6164 converts the encoded bipolar 64kbps signal to dual-rail active-low logic levels. These signals are applied to the XR-T6165 receiver S+R (pin 1) and S-R (pin 2) inputs. A 128kHz clock, which is derived from the received signal, is used to decode this data, and then to clock it into one of two storage registers. Two registers are used so that one may be receiving continuous data at 64kbps while the other is sending eight bit bursts at a 2.048Mbps rate to PCMOUT (pin 21) while the receiver time-slot signal is high. The time-slot is an envelope derived externally from RX2MHz that covers eight clock pulses. The rising edge of the time-slot signal should be made to coincide with the rising edge of RX2MHz. Eight bits of PCM data are clocked out of the receiver register on the rising edge of RX2MHz while the time-slot signal is high. A two input multiplexer at the time-slot input allows the receiver to be hard wired to two time-slot positions.

time-slot signals are applied to TS1R (pin 18) and TS2R (pin 19) and the active time-slot is selected by TSEL (pin 20). A high level applied to RTSEL selects TS1R and a low level selects TS2R. Data appearing at PCMOUT is framed by the read time-slot signal and is guaranteed glitch free.

Recovery of the 128kHz timing signal is performed by a variable length counter which is clocked by the 2.048 MHz signal applied to RXCK2MHz (pin 7). This clock is not required to be synchronized with any other signals that are applied to the XR-T6165. However , the RX2MHz clock (pin 4) may also be used for this function. Positive input data transitions are used toynchronize this counter with the data. If synchronization is lost, the counter length is shortened, and the clock recovery circuit enters a seek mode until a transition is found.

Octet timing ensures that bit grouping is maintained when the data is converted from a 64kbps continuous stream to eight bit 2.048Mbps bursts. Bipolar violations are used to identify the last bit in each eight bit octet. In the absence of required by the XR-T6165. The XR-T6165 then performs these violations, for example when receiving a transmitted alarm condition (transmitter ALARMIN is high), the circuit will continue to operate in synchronization with respect to the last received violation. During this time, the data present at PCMOUT is correct as long as synchronization based on the last received violation is still valid, and the BLS input (pin 3) is held high. However, if BLS is low and an octet timing violation is not received, receiver output data is blanked by forcing PCMOUT to a high level. Also, if eight successive octet timing violations are not received, the ALARM output (pin 22) goes to a high level. A high level applied to the BLANK input (pin 5) will also force PCMOUT to an all-ones state.

Slip control logic is included in the receiver to accommodate rate differences between input and output data. The 64kbps input rate is determined by the remote transmitter, while the PCMOUT rate is set by RX2MHz which is a local clock. If thisclock is slow, an octet will be deleted periodically, while the last octet will be repeated under fast conditions. Octet timing is maintained during these operations.

## **APPLICATION INFORMATION**

/ / / / / /

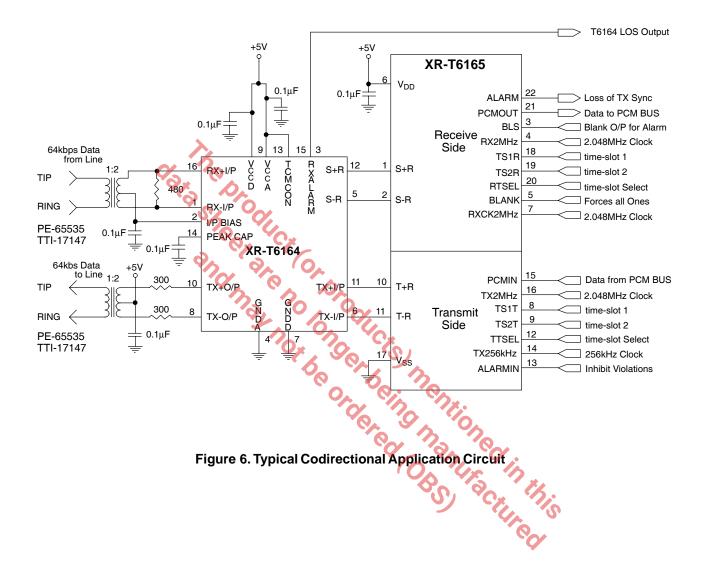

# 64kbps Codirectional Interface

Figure 6 shows a codirectional interface circuit using the XR-T6165 with the XR-T6164 line interface. The XR-T6164 first converts the bipolar 64kbps transmit and receive signals to active-low TTL compatible data the digital functions that are necessary to interface this 64kbps continuous data to a 2.048Mbps PCM time-slot.

The 64kbps signals that have been attenuated and distorted by the twisted pair cable are transformer-coupled to the line side of the XR-T6164 as shown on the left side of Figure 6. A suggested transformer for both the input and output applications is the pulse type PE-65535.

The right side of Figure 6 shows the XR-T6164 LOS (Loss of Signal) output and the XR-T6165 digital inputs and outputs. All of these pins are TTL compatible. Please refer to the pin description section of this data sheet for detailed information about each signal.

## **Transmitter Code Conversion**

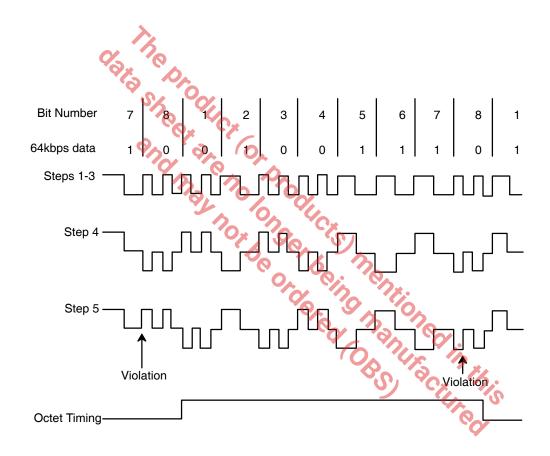

Figure 7 shows the transmitter code conversion process that CCITT G.703 specifies for a 64kbps codirectional interface.

**Step 1** - A 64kbps bit period is divided into four unit intervals.

Step 2 - A binary 1 is coded as a 1100.

Step 3 - A binary 0 is coded as a 1010.

**Step 4** - The binary signal is converted into a three-level signal by alternating the polarity of consecutive blocks.

**Step 5** - The alternation in polarity of the blocks is violated every eighth block. The violation block marks the last bit in an octet.

Figure 7. Transmitter Code Conversion for a 64kbps Bipolar Line Signal

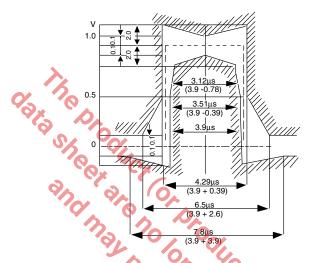

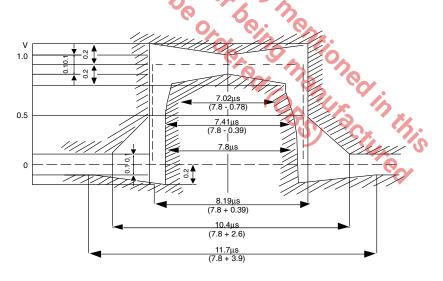

## **Codirectional Interface Pulse Masks**

Figure 8 and Figure 9 show the CCITT G.703 64kbps codirectional interface pulse masks for single and double

pulses respectively of either polarity. Note that this mask is for the pulse measured at the XR-T6164 transmitter output (application circuit shown in *Figure 6*) when terminated with a  $120\Omega$  resistor.

Figure 8. Mask for a Single Pulse

Figure 9. Mask for Double Pulse

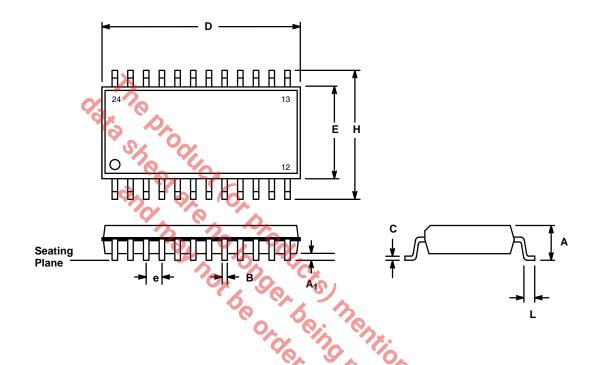

# 24 LEAD SMALL OUTLINE (300 MIL JEDEC SOIC)

|        | INC   | HES    | MILLIMETERS |        |  |

|--------|-------|--------|-------------|--------|--|

| SYMBOL | MIN   | MAX    | MIN         | MAX    |  |

| Α      | 0.093 | 0.104  | 2.35        | 2.65   |  |

| A1     | 0.004 | 0.012  | 0.10        | 0.30   |  |

| В      | 0.013 | 0.020  | 0.33        | 0.51   |  |

| С      | 0.009 | 0.013  | 0.23        | 0.32   |  |

| D      | 0.598 | 0.614  | 15.20       | 15.60  |  |

| Е      | 0.291 | 0.299  | 7.40        | 7.60   |  |

| е      | 0.0   | 50 BSC | 1.2         | 27 BSC |  |

| Н      | 0.394 | 0.419  | 10.00       | 10.65  |  |

| L      | 0.016 | 0.050  | 0.40        | 1.27   |  |

# **Notes**

data sheet are no longer being mentioned in this of the ordered (OBS) actured

NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability EXAR Corporation assumes no responsibility for the use of any circuits de-

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained herein are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or efectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 3121 EXAR Corporation Datasheet EFD 3121

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.

**T**⊕M<sup>™</sup>